|

Register File

A register file is an array of processor registers in a central processing unit (CPU). The instruction set architecture of a CPU will almost always define a set of registers which are used to stage data between memory and the functional units on the chip. The register file is part of the architecture and visible to the programmer, as opposed to the concept of transparent caches. In simpler CPUs, these ''architectural registers'' correspond one-for-one to the entries in a physical register file (PRF) within the CPU. More complicated CPUs use register renaming, so that the mapping of which physical entry stores a particular architectural register changes dynamically during execution. Modern integrated circuit-based register files are usually implemented by way of fast static RAMs with multiple ports. Such RAMs are distinguished by having dedicated read and write ports, whereas ordinary multiported SRAMs will usually read and write through the same ports. Register banking is th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Integer (computer Science)

In computer science, an integer is a datum of integral data type, a data type that represents some interval (mathematics), range of mathematical integers. Integral data types may be of different sizes and may or may not be allowed to contain negative values. Integers are commonly represented in a computer as a group of binary digits (bits). The size of the grouping varies so the set of integer sizes available varies between different types of computers. Computer hardware nearly always provides a way to represent a processor word size, register or memory address as an integer. Value and representation The ''value'' of an item with an integral type is the mathematical integer that it corresponds to. Integral types may be ''unsigned'' (capable of representing only non-negative integers) or ''signed'' (capable of representing negative integers as well). An integer value is typically specified in the source code of a program as a sequence of digits optionally prefixed with + or −. S ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

MMX (instruction Set)

MMX is a ''single instruction, multiple data'' (SIMD) instruction set architecture designed by Intel, introduced on January 8, 1997 with its Pentium P5 (microarchitecture) based line of microprocessors, named "Pentium with MMX Technology". It developed out of a similar unit introduced on the Intel i860, and earlier the Intel i750 video pixel processor. MMX is a processor supplementary capability that is supported on IA-32 processors by Intel and other vendors . AMD also added MMX instruction set in its AMD K6, K6 processor. ''The New York Times'' described the initial push, including Super Bowl advertisements, as focused on "a new generation of glitzy multimedia products, including videophones and 3-D video games." MMX has subsequently been extended by several programs by Intel and others: 3DNow!, Streaming SIMD Extensions (SSE), and ongoing revisions of Advanced Vector Extensions (AVX). Overview Naming MMX is officially a meaningless initialism trademarked by Intel; unoffici ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Pentium

Pentium is a series of x86 architecture-compatible microprocessors produced by Intel from 1993 to 2023. The Pentium (original), original Pentium was Intel's fifth generation processor, succeeding the i486; Pentium was Intel's flagship processor line for over a decade until the introduction of the Intel Core line in 2006. Pentium-branded processors released from 2009 onwards were considered entry-level products positioned above the low-end Intel Atom, Atom and Celeron series, but below the faster Core lineup and workstation/server Xeon series. The later Pentiums, which have little more than their name in common with earlier Pentiums, were based on both the architecture used in Atom and that of Core processors. In the case of Atom architectures, Pentiums were the highest performance implementations of the architecture. Pentium processors with Core architectures prior to 2017 were distinguished from the faster, higher-end i-series processors by lower clock rates and disabling ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Simultaneous Multithreading

Simultaneous multithreading (SMT) is a technique for improving the overall efficiency of superscalar CPUs with hardware multithreading. SMT permits multiple independent threads of execution to better use the resources provided by modern processor architectures. Details The term ''multithreading'' is ambiguous, because not only can multiple threads be executed simultaneously on one CPU core, but also multiple tasks (with different page tables, different task state segments, different protection rings, different I/O permissions, etc.). Although running on the same core, they are completely separated from each other. Multithreading is similar in concept to preemptive multitasking but is implemented at the thread level of execution in modern superscalar processors. Simultaneous multithreading (SMT) is one of the two main implementations of multithreading, the other form being temporal multithreading (also known as super-threading). In temporal multithreading, only one thre ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

POWER8

POWER8 is a family of superscalar multi-core microprocessors based on the Power ISA, announced in August 2013 at the Hot Chips conference. The designs are available for licensing under the OpenPOWER Foundation, which is the first time for such availability of IBM's highest-end processors. Systems based on POWER8 became available from IBM in June 2014. Systems and POWER8 processor designs made by other OpenPOWER members were available in early 2015. Design POWER8 is designed to be a massively multithreaded chip, with each of its cores capable of handling eight hardware threads simultaneously, for a total of 96 threads executed simultaneously on a 12-core chip. The processor makes use of very large amounts of on- and off-chip eDRAM caches, and on-chip memory controllers enable very high bandwidth to memory and system I/O. For most workloads, the chip is said to perform two to three times as fast as its predecessor, the POWER7. POWER8 chips comes in 6- or 12-core variants; each ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

MIPS Technologies

MIPS Tech LLC, formerly MIPS Computer Systems, Inc. and MIPS Technologies, Inc., is an American Fabless semiconductor company, fabless semiconductor design company that is most widely known for developing the MIPS architecture and a series of Reduced instruction set computer, RISC Central processing unit, CPU chips based on it. MIPS provides Microprocessor, processor architectures and cores for digital home, networking, embedded, Internet of things and mobile applications. MIPS was founded in 1984 to commercialize the work being carried out at Stanford University on the MIPS architecture, a pioneering RISC design. The company generated intense interest in the late 1980s, seeing design wins with Digital Equipment Corporation (DEC) and Silicon Graphics (SGI), among others. By the early 1990s the market was crowded with new RISC designs and further design wins were limited. The company was purchased by SGI in 1992, by that time its only major customer, and won several new designs in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

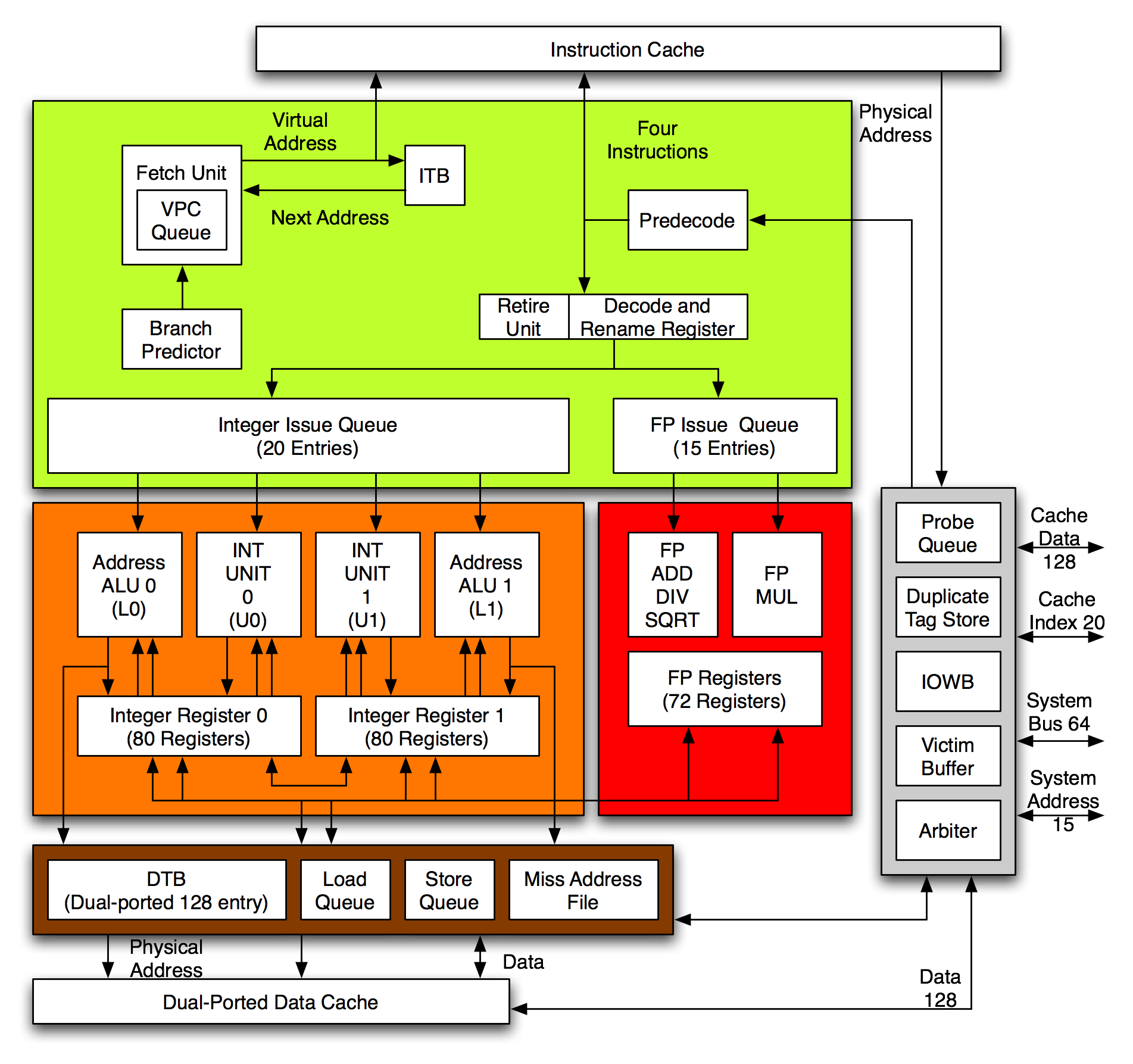

Alpha 21264

The Alpha 21264, also known by its code name, EV6, is a RISC microprocessor developed by Digital Equipment Corporation launched on 19 October 1998. The 21264 implemented the Alpha instruction set architecture (ISA). Description The Alpha 21264 is a four-issue superscalar microprocessor with out-of-order execution and speculative execution. It has a peak execution rate of six instructions per cycle and could sustain four instructions per cycle. It has a seven-stage instruction pipeline. Out of order execution At any given stage, the microprocessor could have up to 80 instructions in various stages of execution, surpassing any other contemporary microprocessor. Decoded instructions are held in instruction queues and are issued when their operands are available. The integer queue contained 20 entries and the floating-point queue 15. Each queue could issue as many instructions as there were pipelines. Ebox The Ebox executes integer, load and store instructions. It has tw ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

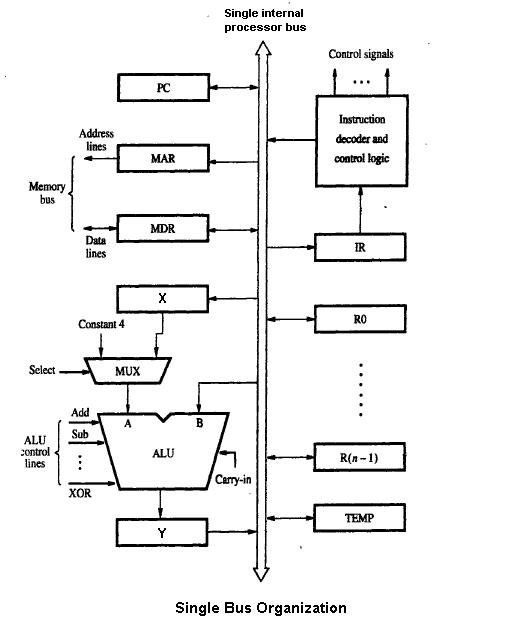

Datapath

A data path is a collection of functional units such as arithmetic logic units (ALUs) or multipliers that perform data processing operations, registers, and buses. Along with the control unit it composes the central processing unit (CPU). A larger data path can be made by joining more than one data paths using multiplexers. A data path is the ALU, the set of registers, and the CPU's internal bus(es) that allow data to flow between them. The simplest design for a CPU uses one common internal bus. Efficient addition requires a slightly more complicated three-internal-bus structure. Many relatively simple CPUs have a 2-read, 1-write register file connected to the 2 inputs and 1 output of the ALU. During the late 1990s, there was growing research in the area of reconfigurable data paths—data paths that may be re-purposed at run-time using programmable fabric—as such designs may allow for more efficient processing as well as substantial power savings. Finite-state machi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Low-power Electronics

Low-power electronics are electronics designed to consume less electrical power than usual, often at some expense. For example, notebook processors usually consume less power than their desktop counterparts, at the expense of computer performance. History Watches The earliest attempts to reduce the amount of power required by an electronic device were related to the development of the wristwatch. Electronic watches require electricity as a power source, and some mechanical movements and hybrid electromechanical movements also require electricity. Usually, the electricity is provided by a replaceable battery. The first use of electrical power in watches was as a substitute for the mainspring, to remove the need for winding. The first electrically powered watch, the Hamilton Electric 500, was released in 1957 by the Hamilton Watch Company of Lancaster, Pennsylvania. The first quartz wristwatches were manufactured in 1967, using analog hands to display the time. Eric A. Vi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |