|

IBM POWER Instruction Set Architecture

IBM POWER is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by IBM. The name is an acronym for ''Performance Optimization With Enhanced RISC''. The ISA is used as base for high end microprocessors from IBM during the 1990s and were used in many of IBM's servers, minicomputers, workstations, and supercomputers. These processors are called POWER1 (RIOS-1, RIOS.9, RSC, RAD6000) and POWER2 (POWER2, POWER2+ and P2SC). The ISA evolved into the PowerPC instruction set architecture and was deprecated in 1998 when IBM introduced the POWER3 processor that was mainly a 32/64-bit PowerPC processor but included the IBM POWER architecture for backwards compatibility. The original IBM POWER architecture was then abandoned. PowerPC evolved into the third Power ISA in 2006. IBM continues to develop PowerPC microprocessor cores for use in their application-specific integrated circuit (ASIC) offerings. Many high volume applications embed PowerPC cores ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Reduced Instruction Set Computer

In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions (more code) in order to accomplish a task because the individual instructions perform simpler operations. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler to achieve given simpler instructions. The key operational concept of the RISC computer is that each instruction performs only one function (e.g. copy a value from memory to a register). The RISC computer usually has many (16 or 32) high-speed, general-purpose registers with a load–store architecture in which the code for the register-register instructions (for performin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Application-specific Integrated Circuit

An application-specific integrated circuit (ASIC ) is an integrated circuit (IC) chip customized for a particular use, rather than intended for general-purpose use, such as a chip designed to run in a digital voice recorder or a high-efficiency video codec. #Application-specific standard product, Application-specific standard product chips are intermediate between ASICs and industry standard integrated circuits like the 7400 series or the 4000 series. ASIC chips are typically semiconductor device fabrication, fabricated using metal–oxide–semiconductor (MOS) technology, as MOS integrated circuit chips. As feature sizes have shrunk and Electronic design automation, chip design tools improved over the years, the maximum complexity (and hence functionality) possible in an ASIC has grown from 5,000 logic gates to over 100 million. Modern ASICs often include entire Central processing unit, microprocessors, memory blocks including Read-only memory, ROM, Random-access memory, RAM, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Emitter-coupled Logic

In electronics, emitter-coupled logic (ECL) is a high-speed integrated circuit bipolar transistor logic family. ECL uses a bipolar junction transistor (BJT) differential amplifier with single-ended input and limited emitter current to avoid the saturated (fully on) region of operation and the resulting slow turn-off behavior. As the current is steered between two legs of an emitter-coupled pair, ECL is sometimes called ''current-steering logic'' (CSL), ''current-mode logic'' (CML) or ''current-switch emitter-follower'' (CSEF) logic. In ECL, the transistors are never in saturation, the input and output voltages have a small swing (0.8 V), the input impedance is high and the output impedance is low. As a result, the transistors change states quickly, gate delays are low, and the fanout capability is high. In addition, the essentially constant current draw of the differential amplifiers minimizes delays and glitches due to supply-line inductance and capacitance, and the compl ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bipolar Junction Transistor

A bipolar junction transistor (BJT) is a type of transistor that uses both electrons and electron holes as charge carriers. In contrast, a unipolar transistor, such as a field-effect transistor (FET), uses only one kind of charge carrier. A bipolar transistor allows a small current injected at one of its terminals to control a much larger current between the remaining two terminals, making the device capable of amplification or switching. BJTs use two p–n junctions between two semiconductor types, n-type and p-type, which are regions in a single crystal of material. The junctions can be made in several different ways, such as changing the doping of the semiconductor material as it is grown, by depositing metal pellets to form alloy junctions, or by such methods as diffusion of n-type and p-type doping substances into the crystal. The superior predictability and performance of junction transistors quickly displaced the original point-contact transistor. Diffused trans ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating-point Arithmetic

In computing, floating-point arithmetic (FP) is arithmetic on subsets of real numbers formed by a ''significand'' (a Sign (mathematics), signed sequence of a fixed number of digits in some Radix, base) multiplied by an integer power of that base. Numbers of this form are called floating-point numbers. For example, the number 2469/200 is a floating-point number in base ten with five digits: 2469/200 = 12.345 = \! \underbrace_\text \! \times \! \underbrace_\text\!\!\!\!\!\!\!\overbrace^ However, 7716/625 = 12.3456 is not a floating-point number in base ten with five digits—it needs six digits. The nearest floating-point number with only five digits is 12.346. And 1/3 = 0.3333… is not a floating-point number in base ten with any finite number of digits. In practice, most floating-point systems use Binary number, base two, though base ten (decimal floating point) is also common. Floating-point arithmetic operations, such as addition and division, approximate the correspond ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Fixed-point Arithmetic

In computing, fixed-point is a method of representing fractional (non-integer) numbers by storing a fixed number of digits of their fractional part. Dollar amounts, for example, are often stored with exactly two fractional digits, representing the cents (1/100 of dollar). More generally, the term may refer to representing fractional values as integer multiples of some fixed small unit, e.g. a fractional amount of hours as an integer multiple of ten-minute intervals. Fixed-point number representation is often contrasted to the more complicated and computationally demanding floating-point representation. In the fixed-point representation, the fraction is often expressed in the same number base as the integer part, but using negative powers of the base ''b''. The most common variants are decimal (base 10) and binary (base 2). The latter is commonly known also as binary scaling. Thus, if ''n'' fraction digits are stored, the value will always be an integer multiple of ' ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Complex Instruction Set Computer

A complex instruction set computer (CISC ) is a computer architecture in which single instructions can execute several low-level operations (such as a load from memory, an arithmetic operation, and a memory store) or are capable of multi-step operations or addressing modes within single instructions. The term was retroactively coined in contrast to reduced instruction set computer (RISC) and has therefore become something of an umbrella term for everything that is not RISC, where the typical differentiating characteristic is that most RISC designs use uniform instruction length for almost all instructions, and employ strictly separate load and store instructions. Examples of CISC architectures include complex mainframe computers to simplistic microcontrollers where memory load and store operations are not separated from arithmetic instructions. Specific instruction set architectures that have been retroactively labeled CISC are System/360 through z/Architecture, the PDP-1 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CDC 6600

The CDC 6600 was the flagship of the 6000 series of mainframe computer systems manufactured by Control Data Corporation. Generally considered to be the first successful supercomputer, it outperformed the industry's prior recordholder, the IBM 7030 Stretch, by a factor of three."Designed by Seymour Cray, the CDC 6600 was almost three times faster than the next fastest machine of its day, the IBM 7030 Stretch." With performance of up to three megaFLOPS, the CDC 6600 was the world's fastest computer from 1964 to 1969, when it relinquished that status to its successor, the CDC 7600."The 7600 design lasted longer than any other supercomputer design. It had the highest performance of any computer from its introduction in 1969 till the introduction of the Cray 1 in 1976." The first CDC 6600s were delivered in 1965 to Livermore and Los Alamos. They quickly became a must-have system in high-end scientific and mathematical computing, with systems being delivered to Couran ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

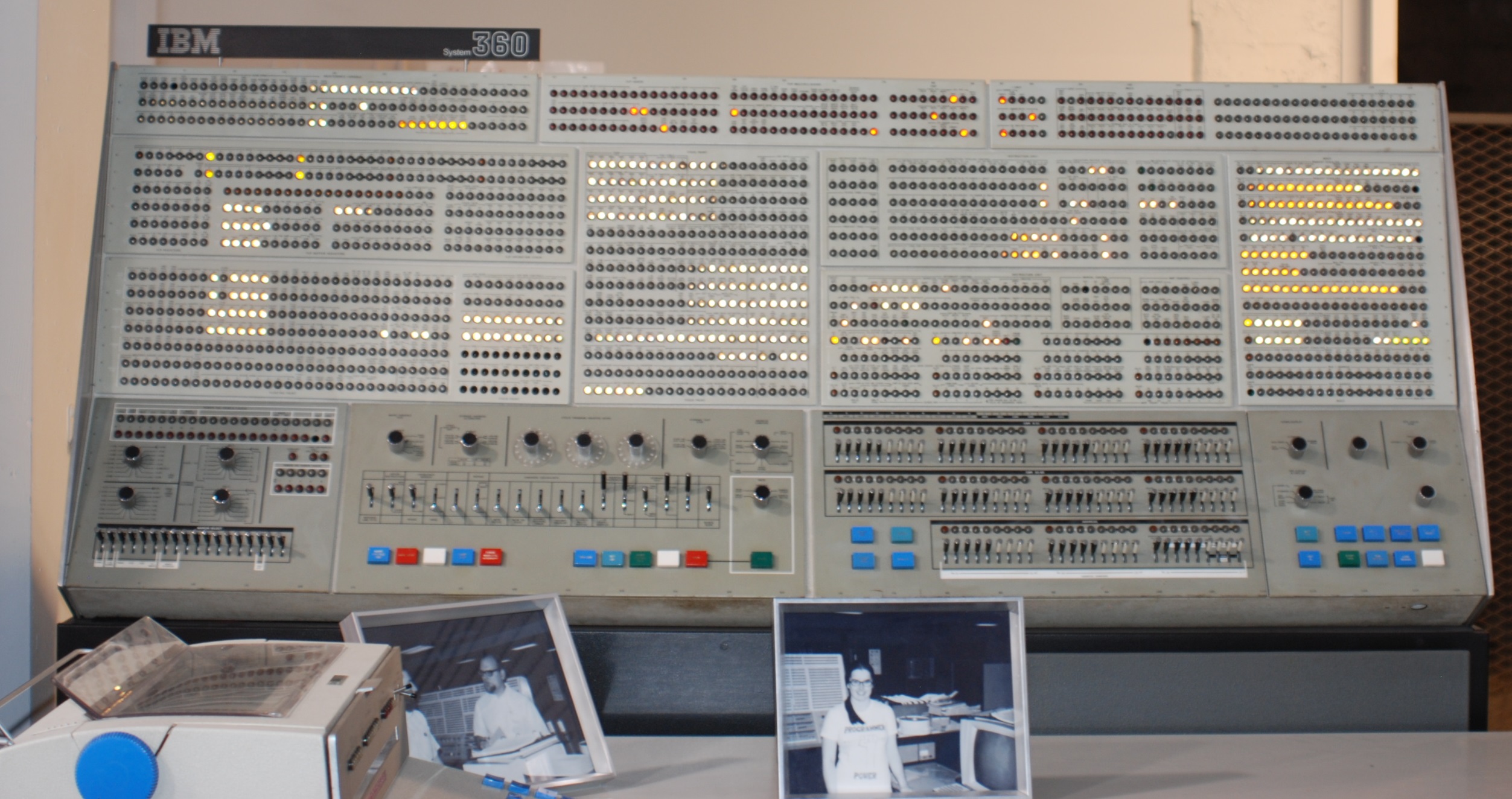

IBM System/360 Model 91

The IBM System/360 Model 91 was announced in 1964 as a competitor to the CDC 6600. Functionally, the Model 91 ran like any other large-scale System/360, but the internal organization was the most advanced of the System/360 line, and it was the first IBM computer to support out-of-order instruction execution. It ran OS/360 as its operating system. It was designed to handle high-speed data processing for scientific applications. This included space exploration, theoretical astronomy, sub-atomic physics and global weather forecasting. The first Model 91 was used at the NASA Goddard Space Flight Center in 1968 and at the time was the most powerful computer in user operation. It was capable of executing up to 16.6 million instructions per second, making it roughly equivalent to an Intel 80486SX-20 MHz CPU or AMD 80386DX-40 MHz CPU in MIPS performance. The CPU consisted of five autonomous units: instruction, floating-point, fixed-point, and two storage controllers for the overlappi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Superscalar

A superscalar processor (or multiple-issue processor) is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a superscalar processor can execute or start executing more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different execution units on the processor. It therefore allows more throughput (the number of instructions that can be executed in a unit of time which can even be less than 1) than would otherwise be possible at a given clock rate. Each execution unit is not a separate processor (or a core if the processor is a multi-core processor), but an execution resource within a single CPU such as an arithmetic logic unit. While a superscalar CPU is typically also pipelined, superscalar and pipelining execution are considered different performance enhancement techni ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Thomas J

Clarence Thomas (born June 23, 1948) is an American lawyer and jurist who has served since 1991 as an associate justice of the Supreme Court of the United States. President George H. W. Bush Clarence Thomas Supreme Court nomination, nominated him to succeed Thurgood Marshall. After Marshall, Thomas is the second African Americans, African American to serve on the U.S. Supreme Court and has been its List of United States Supreme Court justices by time in office, longest-serving member since Anthony Kennedy's retirement in 2018. He has also been the Court's oldest member since Stephen Breyer retired in 2022. Thomas was born in Pin Point, Georgia. After his father abandoned the family, he was raised by his grandfather in a poor Gullah community near Savannah, Georgia. Growing up as a devout Catholic, Thomas originally intended to be a priest in the Catholic Church but became dissatisfied with its efforts to combat racism and abandoned his aspiration to join the clergy. He gradua ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RISC

In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions (more code) in order to accomplish a task because the individual instructions perform simpler operations. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler to achieve given simpler instructions. The key operational concept of the RISC computer is that each instruction performs only one function (e.g. copy a value from memory to a register). The RISC computer usually has many (16 or 32) high-speed, general-purpose registers with a load–store architecture in which the code for the register-register instructions (for performing ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |