|

IBM Enterprise Systems Architecture

IBM Enterprise Systems Architecture is an instruction set architecture introduced by IBM as Enterprise Systems Architecture/370 (ESA/370) in 1988. It is based on the IBM System/370-XA architecture. It extended the dual-address-space mechanism introduced in later IBM System/370 models by adding a new mode in which general-purpose registers 1–15 are each associated with an access register referring to an address space, with instruction operands whose address is computed with a given general-purpose register as a base register will be in the address space referred to by the corresponding address register. The later Enterprise Systems Architecture/390 (ESA/390), introduced in 1990, added a facility to allow device descriptions to be read using channel commands and, in later models, added instructions to perform IEEE 754 floating-point operations and increased the number of floating-point registers from 4 to 16. Enterprise Systems Architecture is essentially a 32-bit architectu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Instruction Set Architecture

In computer science, an instruction set architecture (ISA) is an abstract model that generally defines how software controls the CPU in a computer or a family of computers. A device or program that executes instructions described by that ISA, such as a central processing unit (CPU), is called an ''implementation'' of that ISA. In general, an ISA defines the supported instructions, data types, registers, the hardware support for managing main memory, fundamental features (such as the memory consistency, addressing modes, virtual memory), and the input/output model of implementations of the ISA. An ISA specifies the behavior of machine code running on implementations of that ISA in a fashion that does not depend on the characteristics of that implementation, providing binary compatibility between implementations. This enables multiple implementations of an ISA that differ in characteristics such as performance, physical size, and monetary cost (among other things), but t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Control Register

A control register is a processor register that changes or controls the general behavior of a CPU or other digital device. Common tasks performed by control registers include interrupt control, switching the addressing mode, paging control, and coprocessor control. History The early CPU lacked dedicated control registers, and relied on a limited set of internal signals and flags. When IBM developed a paging version of the System/360, they added 16 control registers to the design for what became the 360/67. IBM did not provide control registers on other S/360 models, but made them a standard part of System/370, although with different register and bit assignments. As IBM added new features to the architecture, e.g., DAS, S/370-XA, S/370-ESA, ESA/390, they added additional fields to the control registers. With z/Architecture, IBM doubled the control register size to 64 bits. Control registers in IBM 360/67 On the 360/67, CR0 and CR2 are used by address translation, CR 4- ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Computing Platforms

A computing platform, digital platform, or software platform is the infrastructure on which software is executed. While the individual components of a computing platform may be obfuscated under layers of abstraction, the ''summation of the required components comprise the computing platform''. Sometimes, the most relevant layer for a specific software is called a computing platform in itself to facilitate the communication, referring to the whole using only one of its attributes – i.e. using a metonymy. For example, in a single computer system, this would be the computer's architecture, operating system (OS), and runtime libraries. In the case of an application program or a computer video game, the most relevant layer is the operating system, so it can be called a platform itself (hence the term cross-platform for software that can be executed on multiple OSes, in this context). In a multi-computer system, such as in the case of offloading processing, it would encompass bo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

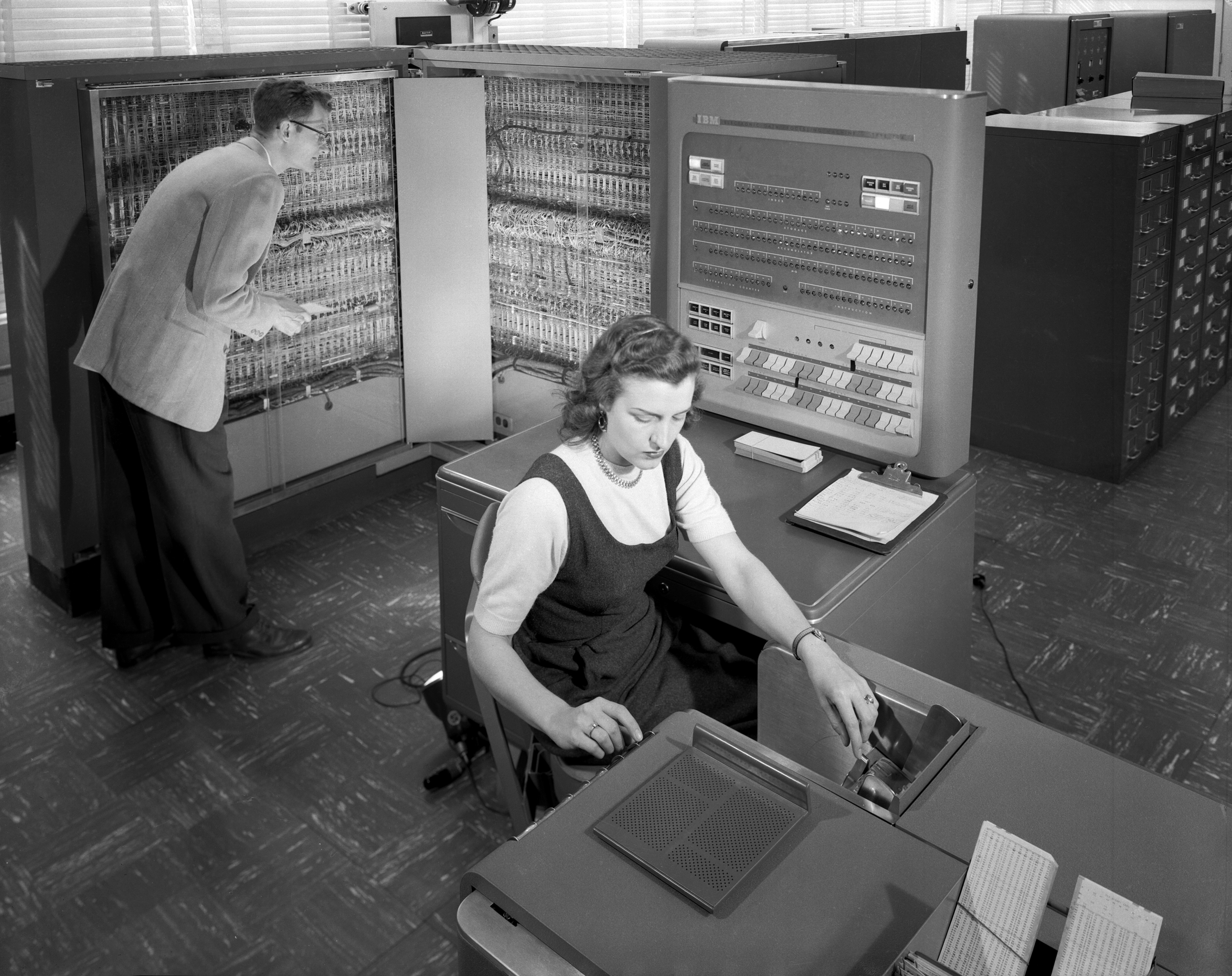

IBM System/360 Mainframe Line

International Business Machines Corporation (using the trademark IBM), nicknamed Big Blue, is an American multinational technology company headquartered in Armonk, New York, and present in over 175 countries. It is a publicly traded company and one of the 30 companies in the Dow Jones Industrial Average. IBM is the largest industrial research organization in the world, with 19 research facilities across a dozen countries; for 29 consecutive years, from 1993 to 2021, it held the record for most annual U.S. patents generated by a business. IBM was founded in 1911 as the Computing-Tabulating-Recording Company (CTR), a holding company of manufacturers of record-keeping and measuring systems. It was renamed "International Business Machines" in 1924 and soon became the leading manufacturer of punch-card tabulating systems. During the 1960s and 1970s, the IBM mainframe, exemplified by the System/360 and its successors, was the world's dominant computing platform, with the company p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Checksum

A checksum is a small-sized block of data derived from another block of digital data for the purpose of detecting errors that may have been introduced during its transmission or storage. By themselves, checksums are often used to verify data integrity but are not relied upon to verify data authenticity. The procedure which generates this checksum is called a checksum function or checksum algorithm. Depending on its design goals, a good checksum algorithm usually outputs a significantly different value, even for small changes made to the input. This is especially true of cryptographic hash functions, which may be used to detect many data corruption errors and verify overall data integrity; if the computed checksum for the current data input matches the stored value of a previously computed checksum, there is a very high probability the data has not been accidentally altered or corrupted. Checksum functions are related to hash functions, fingerprints, randomization functio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Square Root

In mathematics, a square root of a number is a number such that y^2 = x; in other words, a number whose ''square'' (the result of multiplying the number by itself, or y \cdot y) is . For example, 4 and −4 are square roots of 16 because 4^2 = (-4)^2 = 16. Every nonnegative real number has a unique nonnegative square root, called the ''principal square root'' or simply ''the square root'' (with a definite article, see below), which is denoted by \sqrt, where the symbol "\sqrt" is called the '' radical sign'' or ''radix''. For example, to express the fact that the principal square root of 9 is 3, we write \sqrt = 3. The term (or number) whose square root is being considered is known as the ''radicand''. The radicand is the number or expression underneath the radical sign, in this case, 9. For non-negative , the principal square root can also be written in exponent notation, as x^. Every positive number has two square roots: \sqrt (which is positive) and -\sqrt (which i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

PC-based IBM-compatible Mainframes

Since the rise of the personal computer in the 1980s, IBM and other vendors have created PC-based IBM mainframe-compatible systems which are compatible with the larger IBM mainframe computers. For a period of time PC-based mainframe-compatible systems had a lower price and did not require as much electricity or floor space. However, they sacrificed performance and were not as dependable as mainframe-class hardware. These products have been popular with mainframe developers, in education and training settings, for very small companies with non-critical processing, and in certain disaster relief roles (such as field insurance adjustment systems for hurricane relief). Background Up until the mid-1990s, mainframes were very large machines that often occupied entire rooms. The rooms were often air conditioned and had special power arrangements to accommodate the three-phase electric power required by the machines. Modern mainframes are now physically comparatively small and require litt ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Hexadecimal

Hexadecimal (also known as base-16 or simply hex) is a Numeral system#Positional systems in detail, positional numeral system that represents numbers using a radix (base) of sixteen. Unlike the decimal system representing numbers using ten symbols, hexadecimal uses sixteen distinct symbols, most often the symbols "0"–"9" to represent values 0 to 9 and "A"–"F" to represent values from ten to fifteen. Software developers and system designers widely use hexadecimal numbers because they provide a convenient representation of binary code, binary-coded values. Each hexadecimal digit represents four bits (binary digits), also known as a nibble (or nybble). For example, an 8-bit byte is two hexadecimal digits and its value can be written as to in hexadecimal. In mathematics, a subscript is typically used to specify the base. For example, the decimal value would be expressed in hexadecimal as . In programming, several notations denote hexadecimal numbers, usually involving a prefi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

IBM System/390

The IBM System/390 is a discontinued mainframe product family implementing ESA/390, the fifth generation of the System/360 instruction set architecture. The first computers to use the ESA/390 were the Enterprise System/9000 (ES/9000) family, which were introduced in 1990. These were followed by the 9672, Multiprise, and Integrated Server families of System/390 in 1994–1999, using CMOS microprocessors. The ESA/390 succeeded ESA/370, used in the Enhanced 3090 and 4381 "E" models, and the System/370 architecture last used in the IBM 9370 low-end mainframe. ESA/390 was succeeded by the 64-bit z/Architecture in 2000. History On September 5, 1990, IBM published a group of hardware and software announcements, two of which included overviews of three announcements: * System/390 (S/390), as in 360 for 1960s, 370 for 1970s. * Enterprise System/9000 (ES/9000), as in 360 for 1960s, 370 for 1970s. * Enterprise Systems Architecture/390 (ESA/390) was IBM's last 31-bit-address/32 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

IBM Parallel Sysplex

In computing, a Parallel Sysplex is a computer cluster, cluster of IBM mainframes acting together as a single system image with z/OS. Used for disaster recovery, Parallel Sysplex combines data sharing and parallel computing to allow a cluster of up to 32 systems to share a workload for high performance computing, high performance and high availability. Sysplex In 1990, IBM mainframe computers introduced the concept of a Systems Complex, commonly called a Sysplex, with MVS/ESA SPV4.1. This allows authorized components in up to eight logical partitions (LPARs) to communicate and cooperate with each other using the IBM XCF, XCF protocol. Components of a Sysplex include: * A common time source to synchronize all member systems' clocks. This can involve either a Sysplex timer (Model 9037), or the Server Time Protocol (STP) * Global Resource Serialization (GRS), which allows multiple systems to access the same resources concurrently, serializing where necessary to ensure exclusive ac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Hot Chips

French fries, or simply fries, also known as chips, and finger chips (Indian English), are '' batonnet'' or '' julienne''-cut deep-fried potatoes of disputed origin. They are prepared by cutting potatoes into even strips, drying them, and frying them, usually in a deep fryer. Pre-cut, blanched, and frozen russet potatoes are widely used, and sometimes baked in a regular or convection oven, such as an air fryer. French fries are served hot, either soft or crispy, and are generally eaten as part of lunch or dinner or by themselves as a snack, and they commonly appear on the menus of diners, fast food restaurants, pubs, and bars. They are typically salted and may be served with ketchup, vinegar, mayonnaise, tomato sauce, or other sauces. Fries can be topped more heavily, as in the dishes of poutine, loaded fries or chili cheese fries, and are occasionally made from sweet potatoes instead of potatoes. Preparation The standard method for cooking french fries is deep fryi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |