|

Front End Of Line

The front-end-of-line (FEOL) is the first portion of IC fabrication where the individual components (transistors, capacitors, resistors, etc.) are patterned in the semiconductor. FEOL generally covers everything up to (but not including) the deposition of metal interconnect layers. For the CMOS process, FEOL contains all fabrication steps needed to form isolated CMOS elements: # Selecting the type of wafer to be used; Chemical-mechanical planarization and cleaning of the wafer. # Shallow trench isolation (STI) (or LOCOS in early processes, with feature size > 0.25 μm) # Well formation # Gate module formation # Source and drain module formation See also * Back end of line *Integrated circuit An integrated circuit or monolithic integrated circuit (also referred to as an IC, a chip, or a microchip) is a set of electronic circuits on one small flat piece (or "chip") of semiconductor material, usually silicon. Large numbers of tiny ... References Further reading *" ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

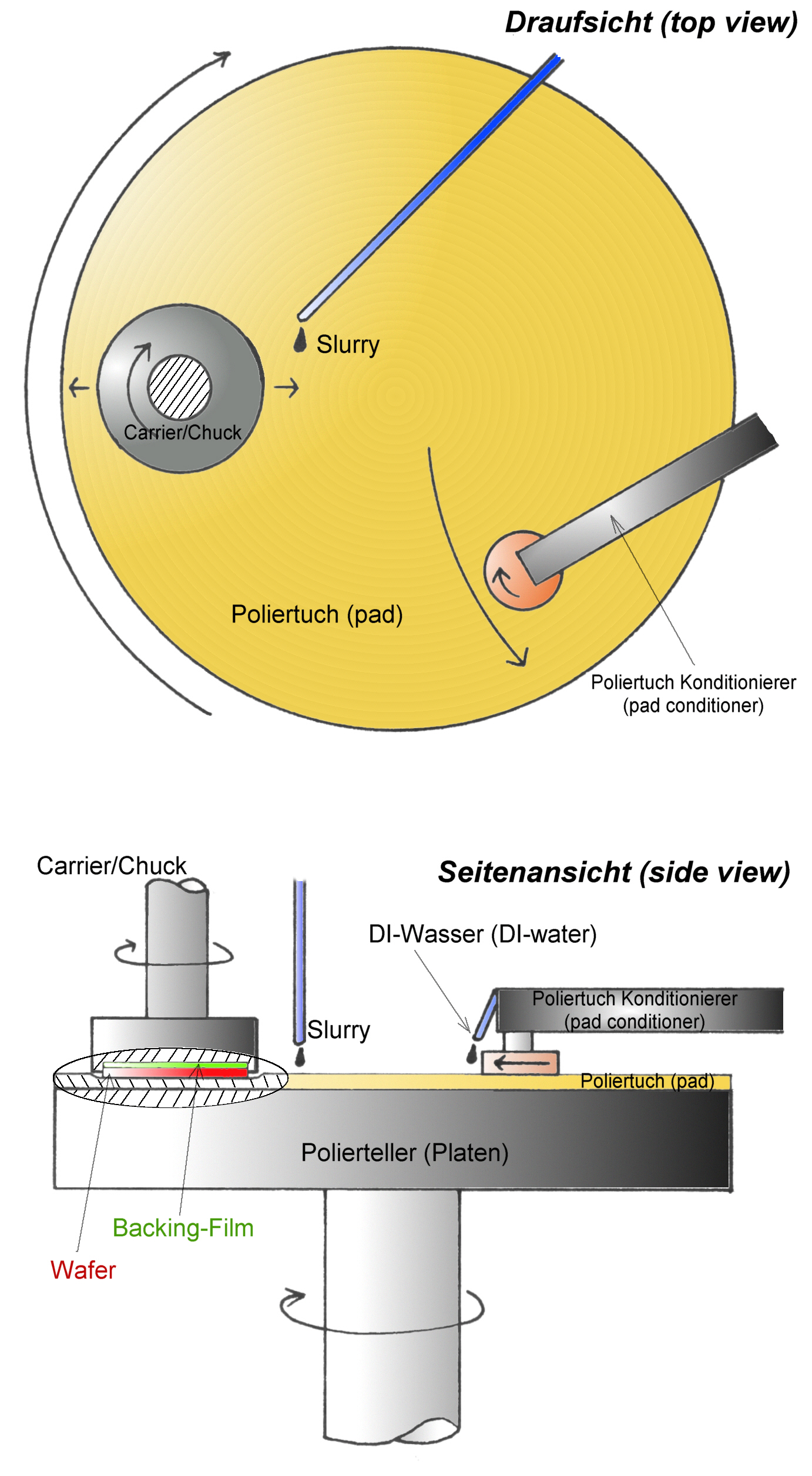

Chemical-mechanical Planarization

Chemical mechanical polishing (CMP) or planarization is a process of smoothing surfaces with the combination of chemical and mechanical forces. It can be thought of as a hybrid of chemical etching and free abrasive polishing. Description The process uses an abrasive and corrosive chemical slurry (commonly a colloid) in conjunction with a polishing pad and retaining ring, typically of a greater diameter than the wafer. The pad and wafer are pressed together by a dynamic polishing head and held in place by a plastic retaining ring. The dynamic polishing head is rotated with different axes of rotation (i.e., not concentric). This removes material and tends to even out any irregular topography, making the wafer flat or planar. This may be necessary to set up the wafer for the formation of additional circuit elements. For example, CMP can bring the entire surface within the depth of field of a photolithography system, or selectively remove material based on its position. Typical depth-o ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Integrated Circuit

An integrated circuit or monolithic integrated circuit (also referred to as an IC, a chip, or a microchip) is a set of electronic circuits on one small flat piece (or "chip") of semiconductor material, usually silicon. Large numbers of tiny MOSFETs (metal–oxide–semiconductor field-effect transistors) integrate into a small chip. This results in circuits that are orders of magnitude smaller, faster, and less expensive than those constructed of discrete electronic components. The IC's mass production capability, reliability, and building-block approach to integrated circuit design has ensured the rapid adoption of standardized ICs in place of designs using discrete transistors. ICs are now used in virtually all electronic equipment and have revolutionized the world of electronics. Computers, mobile phones and other home appliances are now inextricable parts of the structure of modern societies, made possible by the small size and low cost of ICs such as modern computer ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Back End Of Line

The back end of line (BEOL) is the second portion of IC fabrication where the individual devices (transistors, capacitors, resistors, etc.) get interconnected with wiring on the wafer, the metalization layer. Common metals are copper and aluminum. BEOL generally begins when the first layer of metal is deposited on the wafer. BEOL includes contacts, insulating layers (dielectrics), metal levels, and bonding sites for chip-to-package connections. After the last FEOL step, there is a wafer with isolated transistors (without any wires). In BEOL part of fabrication stage contacts (pads), interconnect wires, vias and dielectric structures are formed. For modern IC process, more than 10 metal layers can be added in the BEOL. Steps of the BEOL: # Silicidation of source and drain regions and the polysilicon region. # Adding a dielectric (first, lower layer is pre-metal dielectric (PMD) – to isolate metal from silicon and polysilicon), CMP processing it # Make holes in PMD, make a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

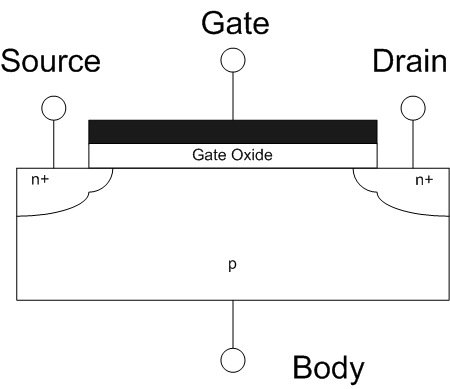

Field-effect Transistor

The field-effect transistor (FET) is a type of transistor that uses an electric field to control the flow of current in a semiconductor. FETs (JFETs or MOSFETs) are devices with three terminals: ''source'', ''gate'', and ''drain''. FETs control the flow of current by the application of a voltage to the gate, which in turn alters the conductivity between the drain and source. FETs are also known as unipolar transistors since they involve single-carrier-type operation. That is, FETs use either electrons (n-channel) or holes (p-channel) as charge carriers in their operation, but not both. Many different types of field effect transistors exist. Field effect transistors generally display very high input impedance at low frequencies. The most widely used field-effect transistor is the MOSFET (metal-oxide-semiconductor field-effect transistor). History The concept of a field-effect transistor (FET) was first patented by Austro-Hungarian physicist Julius Edgar Lilienfeld in 192 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Well Formation

A well is an excavation or structure created in the ground by digging, driving, or drilling to access liquid resources, usually water. The oldest and most common kind of well is a water well, to access groundwater in underground aquifers. The well water is drawn up by a pump, or using containers, such as buckets or large water bags that are raised mechanically or by hand. Water can also be Aquifer storage and recovery, injected back into the aquifer through the well. Wells were first constructed at least eight thousand years ago and historically vary in construction from a simple scoop in the sediment of a dry watercourse to the qanats of Iran, and the stepwells and Sakia, sakiehs of India. Placing a lining in the well shaft helps create stability, and linings of wood or wickerwork date back at least as far as the Iron Age. Wells have traditionally been sunk by hand digging, as is still the case in rural areas of the developing world. These wells are inexpensive and low-tech a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Die Shrink

The term die shrink (sometimes optical shrink or process shrink) refers to the scaling of metal-oxide-semiconductor (MOS) devices. The act of shrinking a die is to create a somewhat identical circuit using a more advanced fabrication process, usually involving an advance of lithographic nodes. This reduces overall costs for a chip company, as the absence of major architectural changes to the processor lowers research and development costs while at the same time allowing more processor dies to be manufactured on the same piece of silicon wafer, resulting in less cost per product sold. Details Die shrinks are the key to improving price/performance at semiconductor companies such as Samsung, Intel, TSMC, and SK Hynix, and fabless manufacturers such as AMD (including the former ATI), NVIDIA and MediaTek. Examples in the 2000s include the downscaling of the PlayStation 2's Emotion Engine processor from Sony and Toshiba (from 180 nm CMOS in 2000 to 90 nm CMOS in 2003), t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LOCOS

LOCOS, short for LOCal Oxidation of Silicon, is a microfabrication process where silicon dioxide is formed in selected areas on a silicon wafer having the Si-SiO2 interface at a lower point than the rest of the silicon surface. As of 2008 it was largely superseded by shallow trench isolation. This technology was developed to insulate MOS transistors from each other and limit transistor cross-talk. The main goal is to create a silicon oxide insulating structure that penetrates under the surface of the wafer, so that the Si-SiO2 interface occurs at a lower point than the rest of the silicon surface. This cannot be easily achieved by etching field oxide. Thermal oxidation of selected regions surrounding transistors is used instead. The oxygen penetrates in depth of the wafer, reacts with silicon and transforms it into silicon oxide. In this way, an immersed structure is formed. For process design and analysis purposes, the oxidation of silicon surfaces can be modeled effectively us ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Shallow Trench Isolation

Shallow trench isolation (STI), also known as box isolation technique, is an integrated circuit feature which prevents electric current leakage between adjacent semiconductor device components. STI is generally used on CMOS process technology nodes of 250 nanometers and smaller. Older CMOS technologies and non-MOS technologies commonly use isolation based on LOCOS. STI is created early during the semiconductor device fabrication process, before transistors are formed. The key steps of the STI process involve etching a pattern of trenches in the silicon, depositing one or more dielectric materials (such as silicon dioxide) to fill the trenches, and removing the excess dielectric using a technique such as chemical-mechanical planarizationbr> Certain semiconductor fabrication technologies also include deep trench isolation, a related feature often found in analog integrated circuits. The effect of the trench edge has given rise to what has recently been termed the "reverse narro ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Wafer (electronics)

In electronics, a wafer (also called a slice or substrate) is a thin slice of semiconductor, such as a crystalline silicon Crystalline silicon or (c-Si) Is the crystalline forms of silicon, either polycrystalline silicon (poly-Si, consisting of small crystals), or monocrystalline silicon (mono-Si, a continuous crystal). Crystalline silicon is the dominant semiconduc ... (c-Si), used for the fabrication of integrated circuits and, in photovoltaics, to manufacture solar cells. The wafer serves as the substrate (materials science), substrate for microelectronic devices built in and upon the wafer. It undergoes many microfabrication processes, such as doping (semiconductor), doping, ion implantation, Etching (microfabrication), etching, thin-film deposition of various materials, and Photolithography, photolithographic patterning. Finally, the individual microcircuits are separated by wafer dicing and Integrated circuit packaging, packaged as an integrated circuit. History I ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CMOS Fabrication Process

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss", ) is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFETs for logic functions. CMOS technology is used for constructing integrated circuit (IC) chips, including microprocessors, microcontrollers, memory chips (including CMOS BIOS), and other digital logic circuits. CMOS technology is also used for analog circuits such as image sensors (CMOS sensors), data converters, RF circuits (RF CMOS), and highly integrated transceivers for many types of communication. The CMOS process was originally conceived by Frank Wanlass at Fairchild Semiconductor and presented by Wanlass and Chih-Tang Sah at the International Solid-State Circuits Conference in 1963. Wanlass later filed US patent 3,356,858 for CMOS circuitry and it was granted in 1967. commercialized the technology with the trademark "COS-MOS" ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CMOS

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss", ) is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFETs for logic functions. CMOS technology is used for constructing integrated circuit (IC) chips, including microprocessors, microcontrollers, memory chips (including CMOS BIOS), and other digital logic circuits. CMOS technology is also used for analog circuits such as image sensors (CMOS sensors), data converters, RF circuits (RF CMOS), and highly integrated transceivers for many types of communication. The CMOS process was originally conceived by Frank Wanlass at Fairchild Semiconductor and presented by Wanlass and Chih-Tang Sah at the International Solid-State Circuits Conference in 1963. Wanlass later filed US patent 3,356,858 for CMOS circuitry and it was granted in 1967. commercialized the technology with the trademark "COS-MO ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)