|

Efficeon

The Efficeon processor is Transmeta's second-generation 256-bit VLIW design released in 2004 which employs a software engine Code Morphing Software (CMS) to convert code written for x86 processors to the native instruction set of the chip. Like its predecessor, the Transmeta Crusoe (a 128-bit VLIW architecture), Efficeon stresses computational efficiency, low power consumption, and a low thermal footprint. Processor Efficeon most closely mirrors the feature set of Intel Pentium 4 processors, although, like AMD Opteron processors, it supports a fully integrated memory controller, a HyperTransport IO bus, and the NX bit, or no-execute x86 extension to PAE mode. NX bit support is available starting with CMS version 6.0.4. Efficeon's computational performance relative to mobile CPUs like the Intel Pentium M is thought to be lower, although little appears to be published about the relative performance of these competing processors. Efficeon came in two package types: a 783- and a 5 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Transmeta Efficeon TM8600 1GHz

Transmeta Corporation was an American fabless semiconductor company based in Santa Clara, California. It developed low power x86 compatible microprocessors based on a VLIW core and a software layer called Code Morphing Software. Code Morphing Software (CMS) consisted of an interpreter, a runtime system and a dynamic binary translator. x86 instructions were first interpreted one instruction at a time and profiled, then depending upon the frequency of execution of a code block, CMS would progressively generate more optimized translations. The VLIW core implemented features specifically designed to accelerate CMS and translations. Among the features were support for general speculation, detection of memory aliasing and detection of self modifying x86 code. The combination of CMS and the VLIW core allowed for the achievement of full x86 compatibility while maintaining performance and reducing power consumption. Transmeta was founded in 1995 by Bob Cmelik, Dave Ditzel, Colin Hunte ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Transmeta

Transmeta Corporation was an American fabless semiconductor company based in Santa Clara, California. It developed low power x86 compatible microprocessors based on a VLIW core and a software layer called Code Morphing Software. Code Morphing Software (CMS) consisted of an Interpreter (computing), interpreter, a runtime system and a Binary translation#Dynamic binary translation, dynamic binary translator. x86 instructions were first interpreted one instruction at a time and profiled, then depending upon the frequency of execution of a code block, CMS would progressively generate more optimized translations. The VLIW core implemented features specifically designed to accelerate CMS and translations. Among the features were support for general speculation, detection of memory aliasing and detection of self modifying x86 code. The combination of CMS and the VLIW core allowed for the achievement of full x86 compatibility while maintaining performance and reducing power consumption. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Code Morphing Software

Transmeta Corporation was an American fabless semiconductor company based in Santa Clara, California. It developed low power x86 compatible microprocessors based on a VLIW core and a software layer called Code Morphing Software. Code Morphing Software (CMS) consisted of an interpreter, a runtime system and a dynamic binary translator. x86 instructions were first interpreted one instruction at a time and profiled, then depending upon the frequency of execution of a code block, CMS would progressively generate more optimized translations. The VLIW core implemented features specifically designed to accelerate CMS and translations. Among the features were support for general speculation, detection of memory aliasing and detection of self modifying x86 code. The combination of CMS and the VLIW core allowed for the achievement of full x86 compatibility while maintaining performance and reducing power consumption. Transmeta was founded in 1995 by Bob Cmelik, Dave Ditzel, Colin Hun ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

256-bit

There are currently no mainstream general-purpose processors built to operate on 256-bit integers or addresses, though a number of processors do operate on 256-bit data. Representation A 256-bit register can store 2256 different values. The range of integer values that can be stored in 256 bits depends on the integer representation used. The maximum value of an unsigned 256-bit integer is 2256 − 1, written in decimal as 115,792,089,237,316,195,423,570,985,008,687,907,853,269,984,665,640,564,039,457,584,007,913,129,639,935 or approximately as 1.1579 x 1077. 256-bit processors could be used for addressing directly up to 2256 bytes. Already 2128 (for 128-bit addressing) would greatly exceed the total data stored on Earth as of 2018, which has been estimated to be around 33.3 zettabytes (over 275 bytes). History Xbox 360 was the first high-definition gaming console to utilize the ATI Technologies 256-bit GPU Xenos before the introduction of the current gaming consoles especially ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Transmeta Crusoe

The Transmeta Crusoe is a family of x86-compatible microprocessors developed by Transmeta and introduced in 2000. Instead of the instruction set architecture being implemented in hardware, or translated by specialized hardware, the Crusoe runs a software abstraction layer, or a virtual machine, known as the Code Morphing Software (CMS). The CMS translates machine code instructions received from programs into native instructions for the microprocessor. In this way, the Crusoe can emulate other instruction set architectures (ISAs). This is used to allow the microprocessors to emulate the Intel x86 instruction set. OS and software limitations as of 2022 The Crusoe processor supports MMX but not SSE. As of 2022, most browsers on Windows and Linux, and some other programs, need SSE or SSE2 support; therefore, that software will no longer run on the Crusoe platform. For example, Firefox dropped support for systems without SSE2 long ago, although K-Meleon could run without SSE on ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier Streaming SIMD Extensions, SSE instruction set, and is intended to fully replace MMX (instruction set), MMX. Intel extended SSE2 to create SSE3 in 2004. SSE2 added 144 new instructions to SSE, which has 70 instructions. Competing chip-maker AMD added support for SSE2 with the introduction of their Opteron and Athlon 64 ranges of x86-64, AMD64 64-bit CPUs in 2003. Features Most of the SSE2 instructions implement the integer vector operations also found in MMX. Instead of the MMX registers they use the XMM registers, which are wider and allow for significant performance improvements in specialized applications. Another advantage of replacing MMX with SSE2 is avoiding the mode switching penalty for issuing x87 instructions present in MMX because it i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

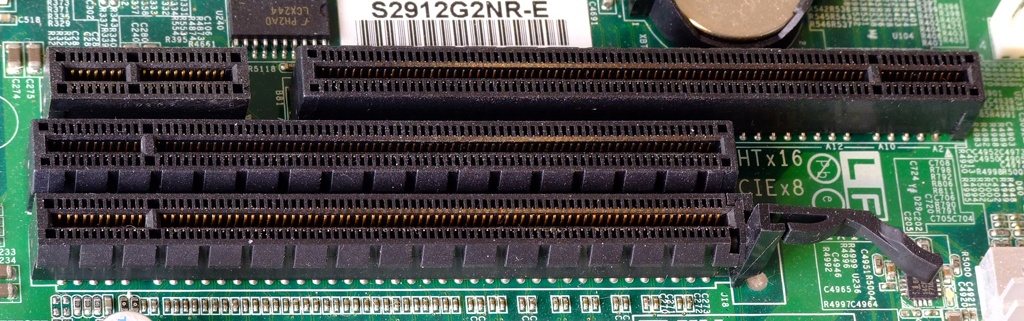

HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/parallel high-bandwidth, low- latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology. HyperTransport is best known as the system bus architecture of AMD central processing units (CPUs) from Athlon 64 through AMD FX and the associated motherboard chipsets. HyperTransport has also been used by IBM and Apple for the Power Mac G5 machines, as well as a number of modern MIPS systems. The current specification HTX 3.1 remained competitive for 2014 high-speed (2666 and 3200 MT/s or about 10.4 GB/s and 12.8 GB/s) DDR4 RAM and slower (around 1 GB/similar to high end Solid-state drive#Standard card form factors, PCIe SSDs ULLtraDIMM flash RAM) technology—a wider range of RAM speeds on a common CPU bus ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating-point

In computing, floating-point arithmetic (FP) is arithmetic that represents real numbers approximately, using an integer with a fixed precision, called the significand, scaled by an integer exponent of a fixed base. For example, 12.345 can be represented as a base-ten floating-point number: 12.345 = \underbrace_\text \times \underbrace_\text\!\!\!\!\!\!^ In practice, most floating-point systems use base two, though base ten (decimal floating point) is also common. The term ''floating point'' refers to the fact that the number's radix point can "float" anywhere to the left, right, or between the significant digits of the number. This position is indicated by the exponent, so floating point can be considered a form of scientific notation. A floating-point system can be used to represent, with a fixed number of digits, numbers of very different orders of magnitude — such as the number of meters between galaxies or between protons in an atom. For this reason, floating-poi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MMX (instruction Set)

MMX is a ''single instruction, multiple data'' (SIMD) instruction set architecture designed by Intel, introduced on January 8, 1997 with its Pentium P5 (microarchitecture) based line of microprocessors, named "Pentium with MMX Technology". It developed out of a similar unit introduced on the Intel i860, and earlier the Intel i750 video pixel processor. MMX is a processor supplementary capability that is supported on IA-32 processors by Intel and other vendors . The New York Times described the initial push, including Super Bowl advertisements, as focused on "a new generation of glitzy multimedia products, including videophones and 3-D video games." MMX has subsequently been extended by several programs by Intel and others: 3DNow!, Streaming SIMD Extensions (SSE), and ongoing revisions of Advanced Vector Extensions (AVX). Overview Naming MMX is officially a meaningless initialism trademarked by Intel; unofficially, the initials have been variously explained as standing for * ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data (SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in their Pentium III series of Central processing units (CPUs) shortly after the appearance of Advanced Micro Devices (AMD's) 3DNow!. SSE contains 70 new instructions (65 unique mnemonics using 70 encodings), most of which work on single precision floating-point data. SIMD instructions can greatly increase performance when exactly the same operations are to be performed on multiple data objects. Typical applications are digital signal processing and graphics processing. Intel's first IA-32 SIMD effort was the MMX instruction set. MMX had two main problems: it re-used existing x87 floating-point registers making the CPUs unable to work on both floating-point and SIMD data at the same time, and it only worked on integers. SSE floating-point instructions operate on a new independent register set, the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sharp PC-MM2 Frontal View

Sharp or SHARP may refer to: Acronyms * SHARP (helmet ratings) (Safety Helmet Assessment and Rating Programme), a British motorcycle helmet safety rating scheme * Self Help Addiction Recovery Program, a charitable organisation founded in 1991 by Barbara Bach and Pattie Boyd * Sexual Harassment/Assault Response & Prevention, a US Army program dealing with sexual harassment * Skinheads Against Racial Prejudice, an anti-racist Trojan skinhead organization formed to combat White power skinheads * Society for the History of Authorship, Reading and Publishing * Stationary High Altitude Relay Platform, a 1980s beamed-power aircraft * Super High Altitude Research Project, a 1990s project to develop a high-velocity gun Companies * I. P. Sharp Associates, a former Canadian computer services company * Sharp Airlines, an Australian regional airline * Sharp Corporation, a Japanese electronics manufacturer * Sharp Entertainment, an American TV program producer * Sharp HealthCare, a hospi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Branch Predictor

In computer architecture, a branch predictor is a digital circuit that tries to guess which way a branch (e.g., an if–then–else structure) will go before this is known definitively. The purpose of the branch predictor is to improve the flow in the instruction pipeline. Branch predictors play a critical role in achieving high performance in many modern pipelined microprocessor architectures such as x86. Two-way branching is usually implemented with a conditional jump instruction. A conditional jump can either be "taken" and jump to a different place in program memory, or it can be "not taken" and continue execution immediately after the conditional jump. It is not known for certain whether a conditional jump will be taken or not taken until the condition has been calculated and the conditional jump has passed the execution stage in the instruction pipeline (see fig. 1). Without branch prediction, the processor would have to wait until the conditional jump instruction has ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |