|

DDR5 SDRAM

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM, DDR5 was planned to reduce power consumption, while doubling bandwidth. The standard, originally targeted for 2018, was released on July 14, 2020. A new feature called Decision Feedback Equalization (DFE) enables I/O speed scalability for higher bandwidth and performance improvement. DDR5 supports more bandwidth than its predecessor, DDR4, with 4.8 gigabits per second possible, but not shipping at launch. DDR5 has about the same latency as DDR4 and DDR3. DDR5 octuples the maximum DIMM capacity from 64 GB to 512 GB. DDR5 also has higher frequencies than DDR4. Rambus announced a working DDR5 DIMM in September 2017. On November 15, 2018, SK Hynix announced completion of its first DDR5 RAM chip; it runs at 5200 MT/s at 1.1 V. In February 2019, SK Hynix announced a 6400 MT/s chip, the highest speed specified by the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Gigabyte

The gigabyte () is a multiple of the unit byte for digital information. The prefix ''giga'' means 109 in the International System of Units (SI). Therefore, one gigabyte is one billion bytes. The unit symbol for the gigabyte is GB. This definition is used in all contexts of science (especially data science), engineering, business, and many areas of computing, including storage capacities of hard drives, solid state drives, and tapes, as well as data transmission speeds. However, the term is also used in some fields of computer science and information technology to denote (10243 or 230) bytes, particularly for sizes of RAM. Thus, prior to 1998, some usage of ''gigabyte'' has been ambiguous. To resolve this difficulty, IEC 80000-13 clarifies that a ''gigabyte'' (GB) is 109 bytes and specifies the term ''gibibyte'' (GiB) to denote 230 bytes. These differences are still readily seen for example, when a 400 GB drive's capacity is displayed by Microsoft Windows as 372 G ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

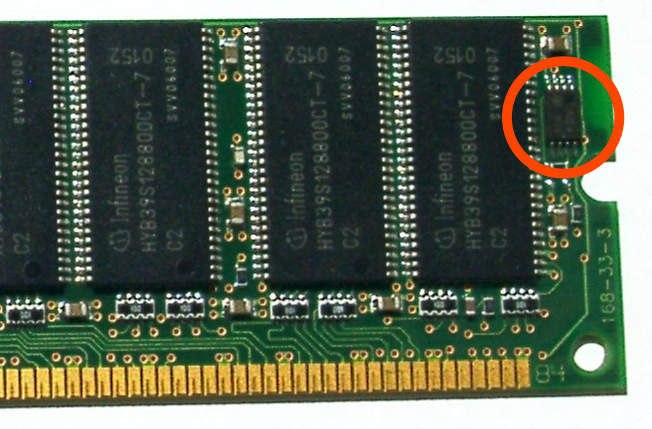

Serial Presence Detect

In computing, serial presence detect (SPD) is a standardized way to automatically access information about a memory module. Earlier 72-pin SIMMs included five pins that provided five bits of ''parallel presence detect'' (PPD) data, but the 168-pin DIMM standard changed to a serial presence detect to encode much more information. When an ordinary modern computer is turned on, it starts by doing a power-on self-test (POST). Since about the mid-1990s, this process includes automatically configuring the hardware currently present. SPD is a memory hardware feature that makes it possible for the computer to know what memory is present, and what memory timings to use to access the memory. Some computers adapt to hardware changes completely automatically. In most cases, there is a special optional procedure for accessing BIOS parameters, to view and potentially make changes in settings. It may be possible to control how the computer uses the memory SPD data—to choose settings, sel ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sapphire Rapids

Sapphire Rapids is a List of Intel codenames, codename for Intel's server (fourth generation Xeon Scalable) and workstation processors based on 7 nm process, Intel 7. Sapphire Rapids was intended as part of the Eagle Stream server platform. In addition, it will be powering Aurora (supercomputer), Aurora, an exascale computing, exascale supercomputer in the United States, at Argonne National Laboratory. History Sapphire Rapids has been a long-standing Intel project in development for over five years and has been subjected to many delays. Sapphire Rapids was first announced by Intel at their Investor Meeting in May 2019 with the intention of Sapphire Rapids succeeding Ice Lake (microprocessor), Ice Lake in 2021. Intel again announced details on Sapphire Rapids in their August 2021 Architecture Day presentation with no mention of a launch date. Intel CEO Pat Gelsinger tacitly blamed the previous Intel leadership as a reason for Sapphire Rapid's many delays. One industry analyst fi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Raptor Lake

Raptor Lake is Intel's codename for the 13th-generation of Intel Core processors based on a hybrid architecture, utilizing Raptor Cove performance cores and Gracemont efficient cores. Raptor Lake launched on October 20, 2022. Mobile versions are expected to be released by the end of the year. Like Alder Lake, Raptor Lake is fabricated using Intel's Intel 7 process. At Intel's Investor Meeting 2022, it was confirmed that Raptor Lake would feature up to 24 cores (8 performance cores plus 16 efficient cores) and 32 threads and is socket compatible with Alder Lake systems (LGA 1700). The company spokesman revealed that Raptor Lake was conjured in the last-minute, to benefit from all the process improvements before Meteor Lake arrives since the next microarchitecture was not ready on time. Raptor Lake competes with the AMD Ryzen 7000 series that was launched about one month earlier on September 27, 2022. Features CPU * Cores ** Raptor Cove performance cores (P-core) ** ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Alder Lake

Alder Lake is Intel's codename for the 12th generation of Intel Core processors based on a hybrid architecture utilizing Golden Cove performance cores and Gracemont efficient cores. It is fabricated using Intel's Intel 7 process, previously referred to as Intel 10 nm Enhanced SuperFin (10ESF). The 10ESF has a 10%-15% boost in performance over the 10SF used in the mobile Tiger Lake processors. Intel officially announced 12th Gen Intel Core CPUs on October 27, 2021. Intel officially announced 12th Gen Intel Core mobile CPUs and non-K series desktop CPUs on January 4, 2022. Intel officially announced the launch of Alder Lake-P and -U series on February 23, 2022, and Alder Lake-HX series on May 10, 2022. History Fabricated using Intel's Intel 7 process, which was previously referred to as Intel 10 nm Enhanced SuperFin (10ESF), Intel officially announced 12th Gen Intel Core CPUs on October 27, 2021. Intel then officially announced 12th Gen Intel Core mobile CPUs and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LPDDR

Low-Power Double Data Rate (LPDDR), also known as LPDDR SDRAM, is a type of synchronous dynamic random-access memory that consumes less power and is targeted for mobile computers and devices such as mobile phones. Older variants are also known as Mobile DDR, and abbreviated as mDDR. Modern LPDDR SDRAM is distinct from DDR SDRAM, with various differences that make the technology more appropriate for the mobile application. LPDDR technology standards are developed independently of DDR standards, with LPDDR4X and even LPDDR5 for example being implemented prior to DDR5 SDRAM and offering far higher data rates than DDR4 SDRAM. Bus width In contrast with standard SDRAM, used in stationary devices and laptops and usually connected over a 64-bit wide memory bus, LPDDR also permits 16- or 32-bit wide channels. The "E" versions mark enhanced versions of the specifications. They formalize overclocking the memory array up to 266 MHz for a 33% performance boost. Memory modules impleme ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

On-die Termination

On-die termination (ODT) is the technology where the termination resistor for impedance matching in transmission lines is located inside a semiconductor chip instead of on a printed circuit board (PCB). Overview of electronic signal termination In lower frequency (slow edge rate) applications, interconnection lines can be modelled as "lumped" circuits. In this case there is no need to consider the concept of "termination". Under the low frequency condition, every point in an interconnect wire can be assumed to have the same voltage as every other point for any instance in time. However, if the propagation delay in a wire, PCB trace, cable, or connector is significant (for example, if the delay is greater than 1/6 of the rise time of the digital signal), the "lumped" circuit model is no longer valid and the interconnect has to be analyzed as a transmission line. In a transmission line, the signal interconnect path is modeled as a circuit containing distributed inductance, capaci ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cache Line

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (M ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ECC Memory

Error correction code memory (ECC memory) is a type of computer data storage that uses an error correction code (ECC) to detect and correct n-bit data corruption which occurs in memory. ECC memory is used in most computers where data corruption cannot be tolerated, like industrial control applications, critical databases, and infrastructural memory caches. Typically, ECC memory maintains a memory system immune to single-bit errors: the data that is read from each word is always the same as the data that had been written to it, even if one of the bits actually stored has been flipped to the wrong state. Most non-ECC memory cannot detect errors, although some non-ECC memory with parity support allows detection but not correction. Description Error correction codes protect against undetected data corruption and are used in computers where such corruption is unacceptable, examples being scientific and financial computing applications, or in database and file servers. ECC can als ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

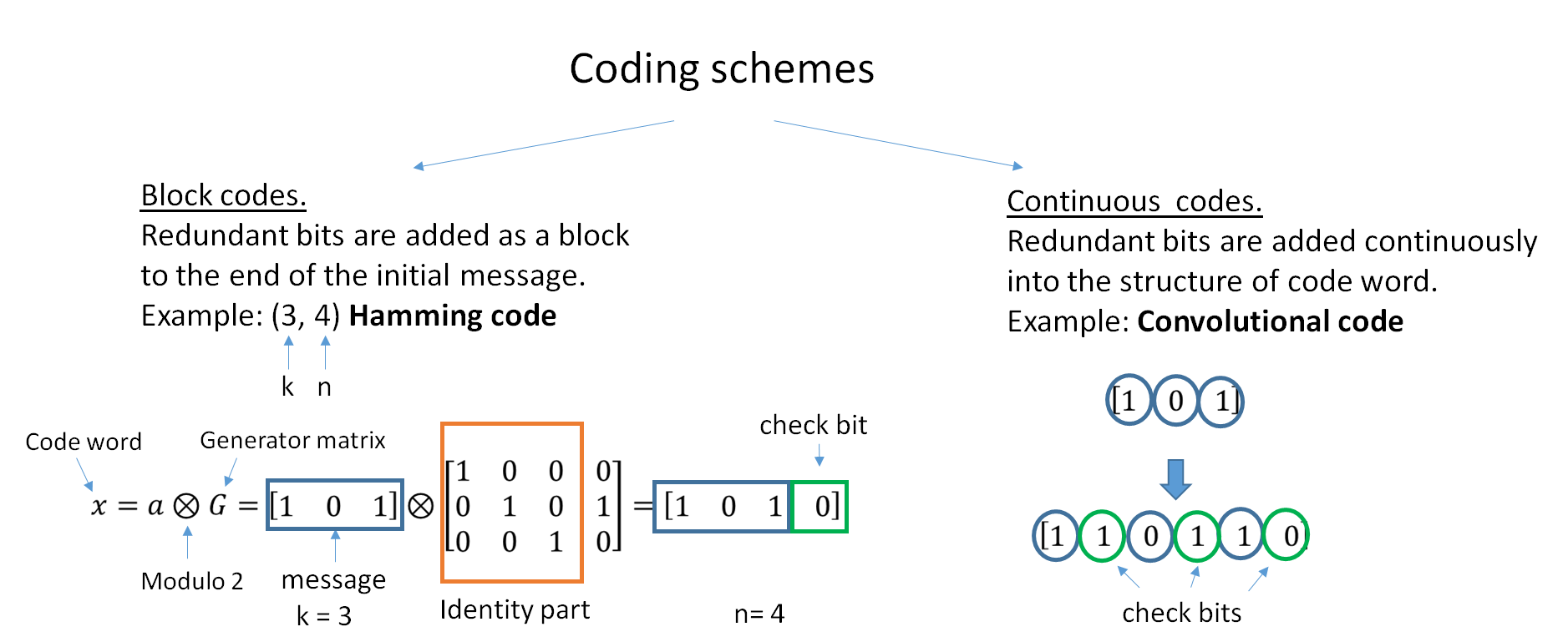

Error-correction Code

In computing, telecommunication, information theory, and coding theory, an error correction code, sometimes error correcting code, (ECC) is used for error control, controlling errors in data over unreliable or noisy communication channels. The central idea is the sender encodes the message with Redundancy (information theory), redundant information in the form of an ECC. The redundancy allows the receiver to detect a limited number of errors that may occur anywhere in the message, and often to correct these errors without retransmission. The American mathematician Richard Hamming pioneered this field in the 1940s and invented the first error-correcting code in 1950: the Hamming (7,4) code. ECC contrasts with error detection in that errors that are encountered can be corrected, not simply detected. The advantage is that a system using ECC does not require a reverse channel to request retransmission of data when an error occurs. The downside is that there is a fixed overhead that is ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Voltage Regulator Module

A voltage regulator module (VRM), sometimes called processor power module (PPM), is a buck converter that provides microprocessor and chipset the appropriate supply voltage, converting , or to lower voltages required by the devices, allowing devices with different supply voltages be mounted on the same motherboard. On personal computer (PC) systems, the VRM is typically made up of power MOSFET devices. Overview Most voltage regulator module implementations are soldered onto the motherboard. Some processors, such as Intel Haswell and Ice Lake CPUs, feature some voltage regulation components on the same CPU package, reduce the VRM design of the motherboard; such a design brings certain levels of simplification to complex voltage regulation involving numerous CPU supply voltages and dynamic powering up and down of various areas of a CPU. A voltage regulator integrated on-package or on-die is usually referred to as ''fully integrated voltage regulator'' (''FIVR'') or simply a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Passive Component

Passivity is a property of engineering systems, most commonly encountered in analog electronics and control systems. Typically, analog designers use ''passivity'' to refer to incrementally passive components and systems, which are incapable of power gain. In contrast, control systems engineers will use ''passivity'' to refer to thermodynamically passive ones, which consume, but do not produce, energy. As such, without context or a qualifier, the term ''passive'' is ambiguous. An electronic circuit consisting entirely of passive components is called a passive circuit, and has the same properties as a passive component. If a component is ''not'' passive, then it is an active component. Thermodynamic passivity In control systems and circuit network theory, a passive component or circuit is one that consumes energy, but does not produce energy. Under this methodology, voltage and current sources are considered active, while resistors, capacitors, inductors, transistors, tunnel di ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |