|

Cyrix III

Cyrix III is an x86-compatible Socket 370 CPU. VIA Technologies launched the processor in February 2000. VIA had purchased both Centaur Technology and Cyrix. Cyrix III was to be based upon a core from one of the two companies. History The Cyrix III was launched in late February 2000. It was initially based on the Joshua core, and was available in two performance ratings of 500 and 533 MHz, with the PR500 being $84 per unit and the PR533 $99. National Semiconductor would be the producer of the chips. 650 and 677 MHz versions of the Cyrix III were available starting January of 2001. The 650 MHz version would cost $55 per chip while the 677 would be $60 and both were based on the Samuel core. The 700 MHz version of the Cyrix III was available on January 19, 2001. The price would be $62 per chip in bulk quantities. This was the last III chip released using the Samuel core, as the Samuel II was expected to be released in March. Just a month later in February 2001, Cyrix III chips ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

National Semiconductor

National Semiconductor was an American semiconductor manufacturer which specialized in analog devices and subsystems, formerly with headquarters in Santa Clara, California. The company produced power management integrated circuits, display drivers, audio and operational amplifiers, communication interface products and data conversion solutions. National's key markets included wireless handsets, displays and a variety of broad electronics markets, including medical, automotive, industrial and test and measurement applications. On September 23, 2011, the company formally became part of Texas Instruments as the "Silicon Valley" division. History Founding National Semiconductor was founded in Danbury, Connecticut, by Dr. Bernard J. Rothlein on May 27, 1959, when he and seven colleagues, Edward N. Clarke, Joseph J. Gruber, Milton Schneider, Robert L. Hopkins, Robert L. Koch, Richard R. Rau and Arthur V. Siefert, left their employment at the semiconductor division of Sperry Rand Corp ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

The Register

''The Register'' is a British technology news website co-founded in 1994 by Mike Magee, John Lettice and Ross Alderson. The online newspaper's masthead sublogo is "''Biting the hand that feeds IT''." Their primary focus is information technology news and opinions. Situation Publishing Ltd is listed as the site's publisher. Drew Cullen is an owner and Linus Birtles is the managing director. Andrew Orlowski was the executive editor before leaving the website in May 2019. History ''The Register'' was founded in London as an email newsletter called ''Chip Connection''. In 1998 ''The Register'' became a daily online news source. Magee left in 2001 to start competing publications ''The Inquirer'', and later the ''IT Examiner'' and ''TechEye''.Walsh, Bob (2007). ''Clear Blogging: How People Blogging Are Changing the World and How You Can Join Them.'' Apress, In 2002, ''The Register'' expanded to have a presence in London and San Francisco, creating ''The Register USA'' at ther ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of VIA Microprocessors

This article lists x86-compliant microprocessors sold by VIA Technologies, grouped by technical merits: cores within same group have much in common. Cyrix design (Cyrix III) * All models support: '' MMX, 3DNow!'' Centaur Technology design Cyrix III, C3 * All models support: '' MMX, 3DNow!'' C3, C7 * All models support: '' MMX, SSE'' * SSE2, SSE3, NX bit supported by Esther (C5J) Nano * See List of Nano microprocessors CHA * Currently in development. Details listed below are subject to change, * 8 cores + "NCORE" neural processor for AI acceleration. * supports: MMX SSE SSE2 SSE3 SSSE3 SSE4.1 SSE4.2 AES AVX AVX2 FMA3 SHA AVX512 AVX512F AVX512CD AVX512BW AVX512DQ AVX512VL AVX512IFMA AVX512VBMI. See also * List of VIA C3 microprocessors * List of VIA C7 microprocessors * List of VIA Eden microprocessors * List of VIA Nano microprocessors References External links Via C3 product pageVia C7 product page Via Nano product page {{VIA VIA ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ceramic Pin Grid Array

A pin grid array (PGA) is a type of integrated circuit packaging. In a PGA, the package is square or rectangular, and the pins are arranged in a regular array on the underside of the package. The pins are commonly spaced 2.54 mm (0.1") apart, and may or may not cover the entire underside of the package. PGAs are often mounted on printed circuit boards using the through hole method or inserted into a socket. PGAs allow for more pins per integrated circuit than older packages, such as dual in-line package (DIP). PGA variants Plastic Plastic pin grid array (PPGA) packaging was used by Intel for late-model Mendocino core Celeron processors based on Socket 370. Some pre-Socket 8 processors also used a similar form factor, although they were not officially referred to as PPGA. Flip chip A flip-chip pin grid array (FC-PGA or FCPGA) is a form of pin grid array in which the die faces downwards on the top of the substrate with the back of the die exposed. This allows ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Square Millimeter

The square metre ( international spelling as used by the International Bureau of Weights and Measures) or square meter (American spelling) is the unit of area in the International System of Units (SI) with symbol m2. It is the area of a square with sides one metre in length. Adding and subtracting SI prefixes creates multiples and submultiples; however, as the unit is exponentiated, the quantities grow exponentially by the corresponding power of 10. For example, 1 kilometre is 103 (one thousand) times the length of 1 metre, but 1 square kilometre is (103)2 (106, one million) times the area of 1 square metre, and 1 cubic kilometre is (103)3 (109, one billion) cubic metres. SI prefixes applied The square metre may be used with all SI prefixes used with the metre. Unicode characters Unicode has several characters used to represent metric area units, but these are for compatibility with East Asian character encodings and are meant to be used in new documents. * * * ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

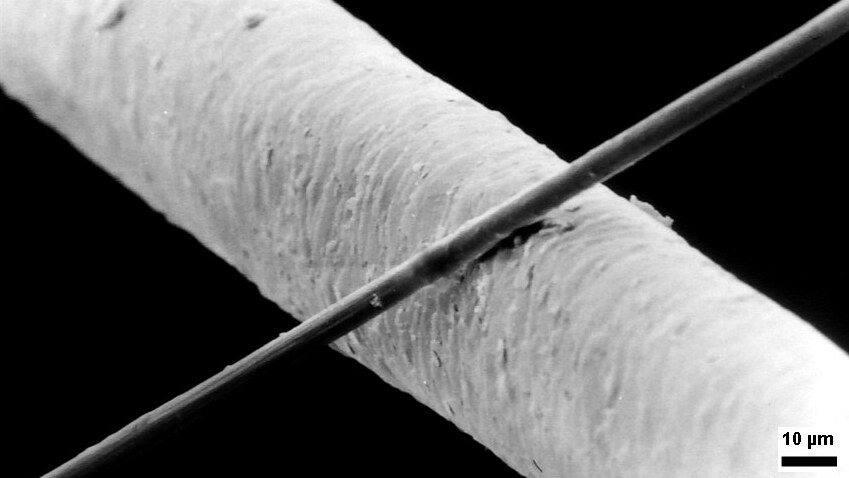

Micrometre

The micrometre ( international spelling as used by the International Bureau of Weights and Measures; SI symbol: μm) or micrometer (American spelling), also commonly known as a micron, is a unit of length in the International System of Units (SI) equalling (SI standard prefix "micro-" = ); that is, one millionth of a metre (or one thousandth of a millimetre, , or about ). The nearest smaller common SI unit is the nanometre, equivalent to one thousandth of a micrometre, one millionth of a millimetre or one billionth of a metre (). The micrometre is a common unit of measurement for wavelengths of infrared radiation as well as sizes of biological cells and bacteria, and for grading wool by the diameter of the fibres. The width of a single human hair ranges from approximately 20 to . The longest human chromosome, chromosome 1, is approximately in length. Examples Between 1 μm and 10 μm: * 1–10 μm – length of a typical bacterium * 3–8 μm – width of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating Point

In computing, floating-point arithmetic (FP) is arithmetic that represents real numbers approximately, using an integer with a fixed precision, called the significand, scaled by an integer exponent of a fixed base. For example, 12.345 can be represented as a base-ten floating-point number: 12.345 = \underbrace_\text \times \underbrace_\text\!\!\!\!\!\!^ In practice, most floating-point systems use base two, though base ten (decimal floating point) is also common. The term ''floating point'' refers to the fact that the number's radix point can "float" anywhere to the left, right, or between the significant digits of the number. This position is indicated by the exponent, so floating point can be considered a form of scientific notation. A floating-point system can be used to represent, with a fixed number of digits, numbers of very different orders of magnitude — such as the number of meters between galaxies or between protons in an atom. For this reason, floating-poin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Performance Rating

The PR (Performance Rating, P-rating) system was a figure of merit developed by AMD, Cyrix, IBM Microelectronics and SGS-Thomson in the mid-1990s (Cyrix announced it in February 1996) as a method of comparing their x86 processors to those of rival Intel. The idea was to consider instructions per cycle (IPC) in addition to the clock speed, so that the processors become comparable with Intel's Pentium that had a higher clock speed with overall lower IPC. Branding The first use of the PR system was in 1995 year, when AMD used it to assert that their AMD 5x86 processor was as fast as a Pentium running at 75 MHz. The designation "P75" was added to the chip to denote this. The letters PR stood for "Performance Rating", but many people mistakenly thought it stood for "Pentium Rating", as the PR was often used to measure performance against Intel's Pentium processor. Later that year, Cyrix also adopted the PR system for its 6x86 and 6x86MX line of processors. These processors were ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instructions Per Cycle

In computer architecture, instructions per cycle (IPC), commonly called instructions per clock is one aspect of a processor's performance: the average number of instructions executed for each clock cycle. It is the multiplicative inverse of cycles per instruction. John L. Hennessy, David A. Patterson.Computer architecture: a quantitative approach. 2007. Explanation While early generations of CPUs carried out all the steps to execute an instruction sequentially, modern CPUs can do many things in parallel. As it is impossible to just keep doubling the speed of the clock, instruction pipelining and superscalar processor design have evolved so CPUs can use a variety of execution units in parallel - looking ahead through the incoming instructions in order to optimise them. This leads to the ''instructions per cycle completed'' being much higher than 1 and is responsible for much of the speed improvements in subsequent CPU generations. Calculation of IPC The calculation of IPC is ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Speculative Execution

Speculative execution is an optimization technique where a computer system performs some task that may not be needed. Work is done before it is known whether it is actually needed, so as to prevent a delay that would have to be incurred by doing the work after it is known that it is needed. If it turns out the work was not needed after all, most changes made by the work are reverted and the results are ignored. The objective is to provide more concurrency if extra resources are available. This approach is employed in a variety of areas, including branch prediction in pipelined processors, value prediction for exploiting value locality, prefetching memory and files, and optimistic concurrency control in database systems.Lazy and Speculative Execution |

Superscalar

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a superscalar processor can execute more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different execution units on the processor. It therefore allows more throughput (the number of instructions that can be executed in a unit of time) than would otherwise be possible at a given clock rate. Each execution unit is not a separate processor (or a core if the processor is a multi-core processor), but an execution resource within a single CPU such as an arithmetic logic unit. In Flynn's taxonomy, a single-core superscalar processor is classified as an SISD processor (single instruction stream, single data stream), though a single-core superscalar processor that supports short vector operations could ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

EDN (magazine)

''EDN'' is an electronics industry website and formerly a magazine owned by AspenCore Media, an Arrow Electronics company. The editor-in-chief is Majeed Ahmad. ''EDN'' was published monthly until, in April 2013, EDN announced that the print edition would cease publication after the June 2013 issue. History The first issue of ''Electrical Design News'', the original name, was published in May 1956 by Rogers Corporation of Englewood, Colorado. In January 1961, Cahners Publishing Company, Inc., of Boston, acquired Rogers Publishing Company. In February 1966, Cahners sold 40% of its company to International Publishing Company in London In 1970, the Reed Group merged with International Publishing Corporation and changed its name to Reed International Limited. Acquisition of ''EEE'' magazine Cahners Publishing Company acquired ''Electronic Equipment Engineering'', a monthly magazine, in March 1971 and discontinued it. In doing so, Cahners folded ''EEE's'' best features into ''EDN'', and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

_CPU-pins_PNr°0295.jpg)